HIGH PERFORMANCE AND EMBEDDED ARCHITECTURE AND COMPILATION

SEVENTH FRAMEWORK

**PROGRAMME**

M. Duranton, D. Black-Schaffer, K. De Bosschere, J. Maebe

This document was produced as a deliverable of the FP7 HiPEAC Network of Excellence under grant agreement 287759. March 2013 The editorial board is indebted to Dr Max Lemke and to Dr Panos Tsarchopoulos of the Complex Systems and Advanced Computing unit of the Directorate-General for Communications Networks, Content and Technology of the European Commission for their active support to this work.

## **CONTENTS**

| CONTENTS                                                       | 1  | 3. TECHNOLOGY CONSTRAINTS                             |    |

|----------------------------------------------------------------|----|-------------------------------------------------------|----|

| EXECUTIVE SUMMARY                                              | 3  | AND OPPORTUNITIES                                     | 2  |

| PREFACE                                                        | 6  | 3.1. CONSTRAINTS                                      | 2  |

|                                                                |    | 3.1.1. HIGH PERFORMANCE HARDWARE BLOCKED              |    |

| 1. ADVANCED COMPUTING SYSTEMS                                  |    | BY THE FOUNDRY COSTS                                  | 2  |

| RECOMMENDATIONS FOR HORIZON 2020                               | 7  | 3.1.2. THE POWER CONSUMPTION COST                     | 2  |

| 1.1. STRATEGIC AREA 1: EMBEDDED SYSTEMS                        | 8  | 3.1.3. COMPLEXITY: THE ACHILLES HEEL OF SOFTWARE      | 3  |

| 1.1.1. COST-EFFECTIVE DESIGN OF EMBEDDED SYSTEMS               | 9  | 3.2. OPPORTUNITIES                                    | 3  |

| 1.1.2. COST-EFFECTIVE CERTIFICATION                            | 9  | 3.2.1. ENTERING THE THIRD DIMENSION                   | 3  |

| 1.1.3. SECURE EMBEDDED SYSTEMS                                 | 9  | 3.2.2. SILICON PHOTONICS                              | 3  |

| 1.2. STRATEGIC AREA 2: DATA CENTER COMPUTING                   | 9  | 3.2.3. WIRELESS CONNECTIVITY                          | 3  |

| 1.2.1. LOW-POWER MICRO SERVERS AND MODULES                     | 9  | 3.2.4. EMERGING MEMORY TECHNOLOGIES                   | 3  |

| 1.2.2. NETWORK AND STORAGE I/O                                 | 10 | 3.2.5. STOCHASTIC/APPROXIMATE COMPUTING               | 3  |

| 1.3. STRATEGIC AREA 3: MOBILE SYSTEMS                          | 10 | 3.2.6. NOVEL ARCHITECTURES                            | 3  |

| 1.3.1. SUPPORTING IMMERSIVE/NATURAL INTERFACES                 | 10 |                                                       |    |

| 1.3.2. ENSURING SECURITY AND PRIVACY FOR PERSONAL DEVICES      | 10 | 4. THE POSITION OF EUROPE                             | 3  |

| 1.4. CROSS-CUTTING CHALLENGE 1: ENERGY EFFICIENCY              | 11 | 4.1. STRENGTHS                                        | 3  |

| 1.5. CROSS-CUTTING CHALLENGE 2: SYSTEM COMPLEXITY              | 12 | 4.1.1. STRONG EMBEDDED ECOSYSTEM                      | 3  |

| 1.6. CROSS-CUTTING CHALLENGE 3: DEPENDABILITY                  | 13 | 4.1.2. PUBLIC FUNDING FOR R&D AND TECHNOLOGY TRANSFER | 3  |

| 1.7. POLICY RECOMMENDATION: SUPPORTING INSTRUMENTS             | 14 | 4.1.3. ONE OF THE BIGGEST MARKETS                     | 3  |

| 1.7.1. SUPPORTING VIRTUAL VERTICALIZATION                      | 14 | 4.1.4. GOOD EDUCATION                                 | 3  |

| 1.7.2. CONTINGENT FUNDING FOR COMMERCIAL DEVELOPMENT           | 14 | 4.2. WEAKNESSES                                       | 3  |

| 1.7.3. CONTINUED FUNDING FOR ACADEMIC RESEARCH                 | 14 | 4.2.1. EUROPE IS FULL OF HORIZONTAL SPECIALIZATION    | 3  |

| 1.7.4. INTERNATIONAL COLLABORATION                             | 14 | 4.2.2. LOSS OF COMPETIVENESS IN SOME DOMAINS          | 3  |

| 1.7.5. DEVELOPING PILOT-LINE FABRICATION CAPABILITIES          | 14 | 4.2.3. BORDERS AND DIFFERENT LANGUAGES                | 3  |

| 1.7.6. LICENSING FOR COLLABORATIVE PROJECTS                    | 14 | 4.2.4. LACK OF VENTURE CAPITALISTS                    | 3  |

|                                                                |    | 4.2.5. WEAK ACADEMIA-INDUSTRY LINK                    | 3  |

| 2. MARKET TRENDS                                               | 17 | 4.3. OPPORTUNITIES                                    | 3  |

| 2.1. APPLICATION PULL: "THE INDUSTRIAL INTERNET"               | 17 | 4.3.1. COST EFFECTIVE CUSTOMIZATION                   | 3  |

| 2.1.1. "POST-PC" DEVICES: THE LINK BETWEEN HUMANS & CYBERSPACE | 18 | 4.3.2. LEVERAGING FREE/CHEAP/OPEN INFRASTRUCTURE      | 3  |

| 2.1.2. NATURAL INTERFACES                                      | 18 | 4.3.3. SOCIETAL CHALLENGES                            | 3  |

| 2.1.3. INTERACTION WITH THE PHYSICAL WORLD                     | 20 | 4.3.4. CONVERGENCE                                    | 4  |

| 2.1.4. DATA DELUGE                                             | 20 | 4.3.5. MICRO- AND NANO-ELECTRONICS                    | 4  |

| 2.1.5. INTELLIGENT PROCESSING                                  | 21 | 4.4. THREATS                                          | 4  |

| 2.1.6. PERSONALIZED SERVICES                                   | 22 | 4.4.1. COMPETING WITH FREE/CHEAP/OPEN INFRASTRUCTURE  | 4  |

| 2.1.7. SENSITIVE/CRITICAL DATA                                 | 23 | 4.4.2. FINANCIAL CRISIS                               | 4  |

| 2.2. BUSINESS TRENDS                                           | 23 |                                                       |    |

| 2.2.1. VERTICAL INTEGRATION WINS                               | 23 | 5. conclusion                                         | 4  |

| 2.2.2. ECONOMY OF SCALE FOR HARDWARE                           | 24 |                                                       |    |

| 2.2.3. CUSTOMER LOCK-IN                                        | 24 | GLOSSARY AND ABBREVIATIONS                            | 4  |

| 2.2.4. CUSTOMER/USER PROFILING                                 | 25 | REFERENCES                                            | 4! |

| 2.2.5. FAB LABS                                                | 25 | SUMMARY                                               | 46 |

## **EXECUTIVE SUMMARY**

Computer performance has increased by over 1,000-fold in the past three decades. This astonishing growth has fueled major innovations across all aspects of society. New advances in drug discovery and diagnosis, product design and manufacturing, transportation and energy, scientific and environmental modeling, social networking and entertainment, financial analysis, all depend on continued increases in computer system performance. Computing systems are so fundamental to today's society that they represent a basic resource, and form a strategic foundation for many of our most powerful and versatile tools and developments. Maintaining rapid growth in computing performance is key for tackling the societal challenges shaping Europe and assuring our global competitiveness in the future.

Yet today we are facing a new set of market trends and technological challenges to this progress, particularly within Europe:

- Market: The dominance of the computing systems market by desktops, laptops, and server PCs is waning and being replaced by a new market of smart embedded systems, mobile devices, and large-scale data centers. This new landscape is moving towards a convergence across embedded, mobile, and data center systems, where *qlobal-scale applications* gather data from embedded systems and users, process it in large data centers, and provide customized, timely information to millions of users through their mobile devices or control our environment ("cyber-physical systems"). Addressing the complexity of system development and data processing at this scale will be critical for the next generation of systems and services. To support these applications, the market has seen a resurgence of verticalization, in which global companies strive to control the whole value chain from chip design through operating systems and applications all the way to end-user data services and sales. Cost and time to market are more than ever keys to

- Technology: Energy has become the primary limiting factor in the development of all systems, whether due to the cost of energy or cooling in large systems or due to battery life in mobile devices. This has led to the rise of parallel and heterogeneous devices that trade off increased complexity and incompatibility with existing software for higher efficiency, and the appearance of "dark silicon", whereby portions of a device must be shut off to stay within the power limit. The necessity to develop energy aware devices and the ability to automate the optimization of applications for power efficiency has

become a necessity across all computing systems.

• European Context: Europe provides a strong embedded and low-power processor ecosystem, which will be critical for addressing power efficiency. This includes many companies in hardware and software development for both the industrial and commercial sectors. However, Europe also suffers from a high degree of horizontal specialization, which makes it difficult for companies to amortize the costs of development across the product chain.

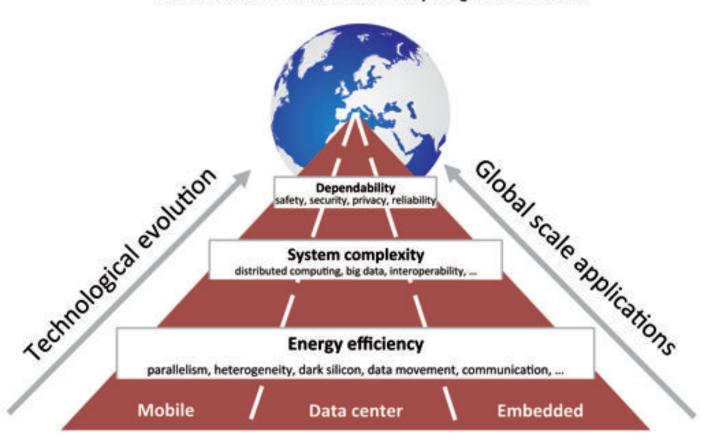

This roadmap dives into the key computing systems challenges facing Europe in the next five years and provides recommendations for strategic research objectives for Horizon 2020. The roadmap leverages the broad academic and industrial expertise of the HiPEAC Network of Excellence to explore technology and market trends and identify promising directions for innovation. This document updates the 2011 roadmap with new trends in market verticalization, global-scale computing, and the impact of hardware design cost, while continuing to emphasize the difficulties of achieving energy-efficiency and programmability across devices from the cloud to mobile and embedded. From this analysis we identify three strategic areas: embedded, mobile, and data center and three cross-cutting challenges: energy efficiency, system complexity, and dependability.

#### **STRATEGIC AREAS FOR HORIZON 2020**

#### • Embedded systems

The traditional notion of an embedded system as a singlepurpose device is rapidly changing as increased computing performance, connectivity and closer interactions with the world bring additional functionality and demands. To take advantage of this potential we need to rethink system architectures and programming models to optimize for energy, time constraints and safety and develop techniques to support portability of critical and mixed critical systems. Without such portability, the cost of certification for new computing platforms will prevent their uptake and limit our ability to leverage further advances.

#### Mobile systems

The shift from desktop PCs to mobile devices provides an incredible opportunity to rethink the human-computer interface and how we interact with technology. Innovations that provide more natural and immersive experiences will dramatically improve the utility and productivity of mobile devices. Such developments require collaboration across all levels of the computing system: from human interaction to image processing and data mining, down to system architecture for efficiency and performance. Further, as mobile devices become increasingly integrated in our public and private lives, we will need stronger guarantees of privacy and security.

#### • Data center computing

As applications become global-scale, Europe has an opportunity to lead the global market for data center technology. To be competitive we must develop the capabilities to process "big data" without increasing cost or energy. These challenges include architectures for handling massive unstructured data sets, low-power server modules and standards, network and storage systems, scalable software architectures, and micro servers. At the same time we must integrate these developments with techniques to ensure security, privacy, and compliance, while providing large-scale reliability, availability, and serviceability.

#### **CROSS-CUTTING CHALLENGES FOR HORIZON 2020**

#### • Energy efficiency

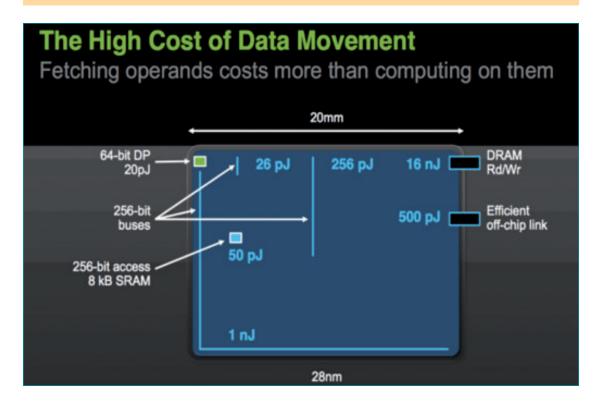

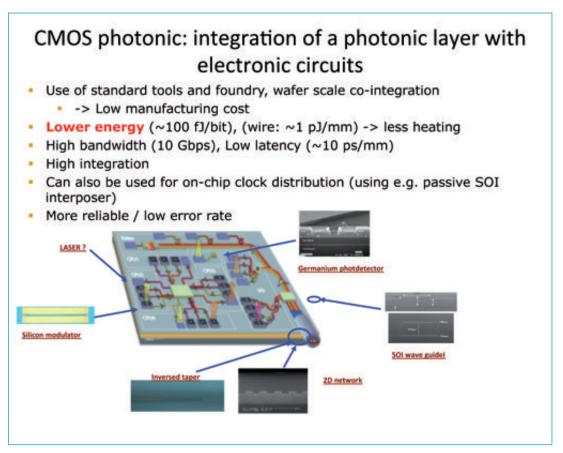

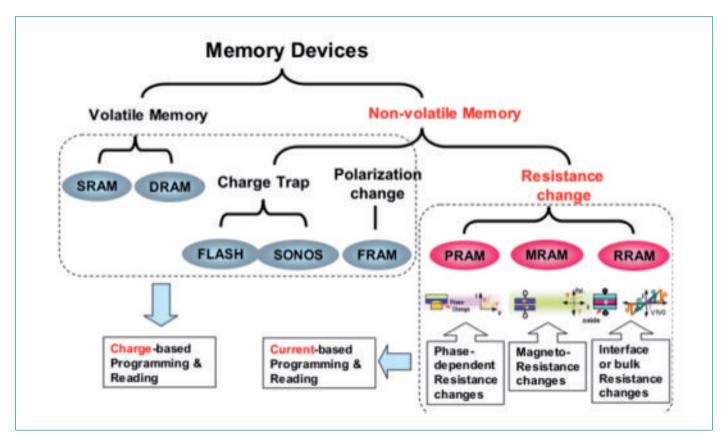

Systems today are limited in their performance by power used or dissipated. This has led to the combination of many specialized (heterogeneous) processors to increase efficiency. Unfortunately, this has also increased the complexity of programming to the point where it is prohibitively expensive for many applications. On top of this, the energy cost of moving data now exceeds that of computing results. To enable power efficient systems we must address the challenges of programming parallel heterogeneous processors and optimizing data movement, both for legacy applications and new computing modalities. We must also take advantage of the energy saving potential of new technologies, such as non-volatile memories, 2.5D and 3D integration techniques, new silicon technologies such as FinFETs and FDSOI, and new computing modalities such as stochastic and approximate systems and algorithms.

#### The HiPEAC vision for Advanced Computing in Horizon 2020

#### • System complexity.

Modern computing systems have grown to the scale where developers need to coordinate thousands of processors at once to accomplish complex tasks for large numbers of users and across massive data sets. To support this scale we need to develop tools and techniques to optimize for performance and ensure correct operation, while operating "at-scale". On the hardware side, chips have become enormously more expensive to design, verify, and produce. Today's cutting-edge technologies are so expensive that they are only affordable for devices that sell 10-100 million units. This cost limits product differentiation and makes market entry for new ideas extremely difficult. To overcome this we need to investigate new integration techniques that enable high levels of integration and differentiation without the cost of cutting-edge fabrication.

#### • Dependability.

Computing systems are involved in ever growing parts of our lives, from providing intelligent control for our transportation to keeping track of our friends and colleagues. As this involvement grows, we require higher levels of dependability. We expect computing systems to be trustable, reliable and secure from malicious attacks, to comply with all safety requirements, and to protect our privacy. Ensuring these properties will require more powerful methodologies and tools to design and implement dependable systems in a cost-effective way.

In addition to the six strategic areas and cross-cutting challenges listed above, HiPEAC recommends several supporting instruments that will improve the effectiveness of Horizon 2020 in stimulating research, startups, industrial uptake. In particular, successful research results should be easily and directly transferred to European industry to address performance, cost, and time-tomarket constraints. Practical recommendations include: the creation of "virtual verticals" by bringing together players across all parts of the product chain - including customers - to tackle key problems, not only scientific ones; encouraging the transfer to real marketable products through contingent funding for commercial development after the completion of STREP projects; extended-length funding of academic research to address the longer duration high-risk projects; carefully selected international collaboration outside of Europe to bring in complementary expertise; the development of pilot-line device fabrication capabilities accessible to SMEs and startups and bridging the gap between research prototypes and products; and analysis of open source licensing frameworks to ensure that EU-funded projects do not release IP under licenses that are incompatible with commercialization.

By addressing these research objectives through Horizon 2020 we will be able to ensure that Europe will continue to benefit from the promised growth of computing technology across all sectors. If we can take the lead in these areas, Europe will be in a position to develop new technologies and standards for the global computing systems market and transfer it to its industry. However, failure to address these challenges will significantly reduce our ability to leverage computing systems to improve our global competitiveness and tackle our social challenges.

The FP7 network of excellence in High Performance and Embedded Architecture and Compilation (HiPEAC) is Europe's premier organization in the field of computing systems for coordinating research, improving mobility, and enhancing visibility. Created in 2004, HiPEAC gathers over 330 leading European academic and industrial computing system researchers from nearly 140 universities and 70 companies in one virtual center of excellence of 1200 researchers. HiPEAC encourages computing innovation in Europe by providing collaboration grants, internships, sabbaticals, and networking through the yearly HiPEAC conference, ACACES summer school, and the semi-annual computing systems week.

## **PREFACE**

Computing systems are universal. All aspects of public, private, and commercial life are affected both directly and indirectly by computing systems. Advances in computing are the key to the development of new domains and revolutionary technologies, such as personalized medicine, online social interaction, and immersive entertainment experiences. Across all of modern society, from manufacturing to agriculture, communications to energy, and social interaction to advanced science, computing systems are our primary tools for improving productivity, safety, well-being, and health. Computing systems play a major role in addressing our major societal challenges, including transportation, mobility, environment, energy conservation and education.

Yet, today computing systems are experiencing several dramatic shifts. Technological limitations are preventing the seemingly effortless performance increases of the past, while global-scale applications are placing computing systems into ever larger, more intensive, and more critical roles. At the same time applications and business trends are broadening the requirements for interoperability and flexibility. Devices have to integrate into global information processing chains, ranging from embedded systems interacting with the physical world, to mobile devices and data center servers for the cloud or High Performance Computing (HPC), always interconnected and communicating. The resulting dramatic increasing complexity, design and technology costs are limiting our ability to expand the impact of computing systems to new domains and applications.

This document is an update of the previous HiPEAC roadmap "Computing Systems: Research Challenges Ahead – the HiPEAC Vision 2011/2012". It focuses on challenges for the coming five years, as formalized in concrete recommendations for the first years of HORIZON 2020. These recommendations are described in the first chapter of this document.

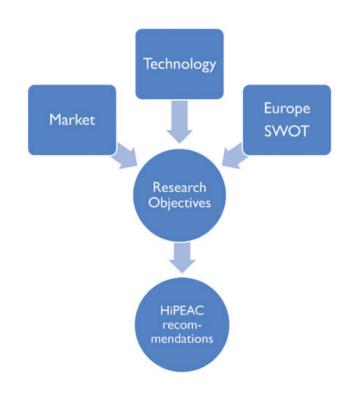

These recommendations are rooted and motivated in the subsequent parts: an analysis of the market trends, a discussion of the technology constraints and opportunities, and a review of Europe's Strengths, Weaknesses, Opportunities, and Threats (SWOT) in the field of computing systems. From this information, the document identifies three strategic areas: embedded, mobile, and data center and three cross-cutting challenges: energy efficiency, system complexity, and dependability, which form the basis for the recommendations.

Structure of the document

#### **ACKNOWLEDGEMENTS**

This document is based on the valuable inputs form the HiPEAC members, the teachers of the ACACES summer school 2012 and the participants of the roadmap meeting during the Computing System Week of October 2012. The editorial board, composed of Marc Duranton (CEA), David Black-Schaffer (Uppsala University), Koen de Bosschere (Ghent University) and Jonas Maebe (Ghent University), would like to particularly thank:

Angelos Bilas (Forth), Robin Bruce (Maxeler), Paolo Faraboschi (HP Labs), Grigori Fursin (INRIA), Christian Gamrat (CEA), Dimitris Gizopoulos (University of Athens), John Goodacre (ARM), Harm Munk (Astron), Marco Ottavi (University of Rome, Tor Vergata), Daniel Gracia Pérez (Thalès), Salvatore Pontarelli (University of Rome, Tor Vergata), Julien Ryckaert (imec), Per Stenström (Chalmers), Joseph van Vlijmen (ACE), Jennifer Sartor (Ghent University).

Computing systems are experiencing a turbulent transition, full of both challenges and opportunities. The landscape of computing devices is changing: traditional desktop and servers are being replaced by mobile devices, smart embedded computing, and global data centers. Ubiquitous wireless communication provides constant access to unlimited amounts of data, thereby opening huge opportunities for novel services and applications, but also presenting significant risks to privacy and security. The convergence of embedded, mobile, and data center computing is moving us towards global-scale systems, which orchestrate thousands of machines, leading to a dramatic increase in system complexity.

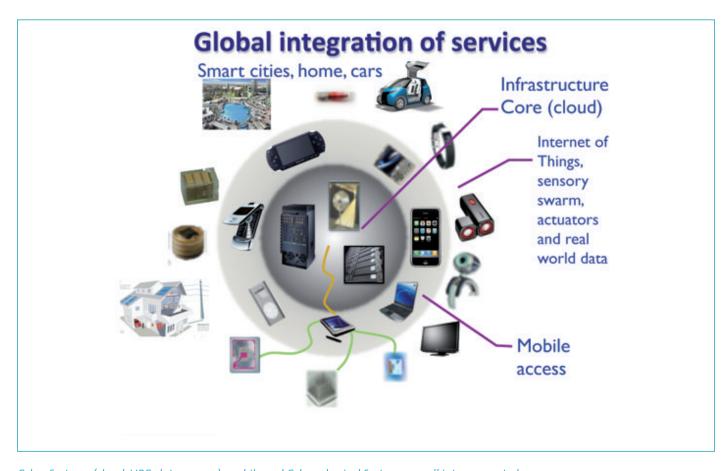

In the future, the "computer" will be the global mesh of data, compute power, and interactivity stemming from the convergence of embedded computing, mobile computing, and data center computing. This integration can be referred to as the "Industrial Internet", where the goal is to serve the user with trustworthy, reliable and safe services to support daily activities and needs.

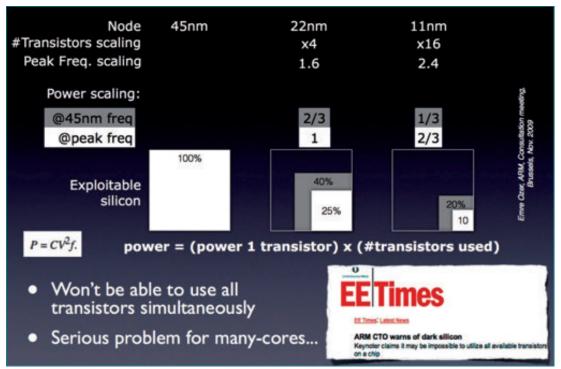

At the same time that the world is shifting towards the convergence of embedded, mobile, and data center computing, the "free lunch" of continuous frequency scaling and power reduction of the past 50 years is over. The continuous performance improvements we have come to depend on have ceased due to the intrinsic power and frequency constraints of ever-smaller transistors. As a result, we are now faced with adapting to the complexities of heterogeneous parallelism in the quest for energy efficiency and increased performance. But the cost to leverage the advances of heterogeneous parallelism is too great for most applications due to the immaturity of software tools and techniques.

European industry and researchers are strong in several of the key technologies required for this future, in particular embedded systems and low-power processors. We believe that Europe should leverage these strengths through investment in tools and technologies to enable the future convergence of data center computing, mobile computing devices, and embedded devices and sensors.

To address these issues, HiPEAC has identified three key strategic areas: mobile, embedded, and data center and three key crosscutting challenges: energy, complexity, and dependability. Addressing these strategic areas and tackling these challenges will require working across system and application boundaries, rethinking hardware and software interfaces, and investigating the impacts of technology and application evolution on algorithms and methodologies.

#### STRATEGIC AREAS

#### • Embedded computing

Embedded computing devices form the interface between the physical world and the digital world. They use sensors and actuators to measure and control physical phenomena, such as temperature, traffic, and electricity usage. Embedded computing devices have local computing power to preprocess raw data and extract salient features in order to reduce communication requirements or to locally process data in order to control actuators. Depending on the application, this computing power can be quite significant (e.g., intelligent surveillance cameras, Engine Control Units (ECUs) controlling the engine in a car) or negligible (e.g., thermostats). Embedded computing devices are ubiquitous. They are typically attached to the physical device they are monitoring and/or controlling, and communicate externally via a wired or wireless network. Embedded computing devices are the building blocks of the *Internet of Things* and of *Cyber-Physical systems*.

#### Mobile computing

Mobile computing devices such as smartphones and tablets form the interface between the *humans* and the *digital world* (or "cyberworld"). The role of mobile devices is to support natural interfaces, which provide humans access to the information stored in the digital world. Mobile devices are responsible for understanding their users' environment, retrieving the most pertinent information, and visualizing the results in an intuitive manner. These devices will actively work to optimize their users' experience by seeking out relevant information, providing a local sensing platform, offering new features.

#### • Data center computing

Data center computing is required to process the massive amounts of data generated by embedded and mobile computing systems, online transactions, and scientific simulations. These systems offer on-demand computing, storage, and scalability, and are backed by geographically distributed infrastructures and resources. The role of data center computing is to provide the computational capacity for analyzing and interpreting the data (e.g., real-time translation, forecasting, scientific computing, etc.) the storage capacity for recording it (e.g., customer activity, environmental conditions, experimental results, etc.) and ubiquitous access and scalability (e.g., to handle peak loads and provide reliability). Taken together, the many computing service providers and the network infrastructure constitute a "global data center". Efficient communication networks are a mandatory element for off-loading computation and data to data center.

#### **CROSS-CUTTING CHALLENGES**

#### • Energy efficiency

Systems today are limited in their performance by power used or dissipated. This has led to the combination of many specialized (heterogeneous) processors to increase efficiency. Unfortunately, this has also increased the complexity of programming to the point where it is prohibitively expensive for many applications. On top of this, the energy cost of moving data now exceeds that of computing results. To enable power efficient systems we must address the challenges of programming parallel heterogeneous processors and optimizing data movement, both for legacy applications and new computing modalities. We must also take advantage of the energy saving potential of new technologies, such as non-volatile memories, 2.5D and 3D integration techniques, new silicon technologies such as FinFETs and FDSOI, and new computing modalities such as stochastic and approximate systems and algorithms.

**System complexity.** Modern computing systems have grown to the scale where developers need to coordinate thousands of processors at once to accomplish complex tasks for large numbers

of users and across massive data sets. To support this scale we need to develop tools and techniques to optimize for performance and ensure correct operation, while operating "at-scale". On the hardware side, chips have become enormously more expensive to design, verify, and produce. Today's cutting-edge technologies are so expensive that they are only affordable for devices that sell 10-100 million units. This cost limits product differentiation and makes market entry for new ideas extremely difficult. To overcome this we need to investigate new integration techniques that enable high levels of integration and differentiation without the cost of cutting-edge fabrication.

#### Dependability

Computing systems are involved in ever growing parts of our lives, from providing intelligent control for our transportation to keeping track of our friends and colleagues. As this involvement grows, we require higher levels of dependability. We expect computing systems to be trustable, reliable and secure from malicious attacks, to comply with all safety requirements, and to protect our privacy. Ensuring these properties will require more powerful methodologies and tools to design and implement cost-effective systems.

Future killer applications will come from the convergence of mobile and embedded interface devices and data center computing. This convergence will enable applications to dynamically redistribute computation and communications depending on the local environment and will operate "at-scale" to handle millions of global users and the processing of enormous data sets. For example, smart embedded computing in roads and vehicles will communicate traffic behavior and intentions. This data will be aggregated and processed in real-time by large-scale compute services. The results will then be personalized and displayed by in-car interfaces to optimize traffic flow. Similar scenarios exist for smart grids, smart cities, health monitoring, industrial automation, and national security. However, these systems must continuously adapt to local communications, power, and processing constraints, by adjusting how compute, sensing, and communications are distributed between the embedded systems, mobile systems, and global data centers. By developing the infrastructure and techniques to develop applications that span all three layers we will be able to benefit from the available data, interactivity, and compute power.

#### 1.1. STRATEGIC AREA 1: EMBEDDED SYSTEMS

Europe is known for its large expertise and experience in the field of embedded systems and it should continue to be at the forefront of innovation in those domains. Competitiveness in this area is essential as the market for embedded systems dwarfs the mobile and data center markets, and is less dominated by non-European vertically integrated companies. Maintaining leadership in advanced embedded computing is a key opportunity for Europe.

Moving forward requires efficiently coping with timing constraints and safety, reducing certification costs, ensuring correctness in more complex systems, and supporting more complex devices. Emphasis should be given to how to design or leverage commodity computer system architectures for efficient support of mixed criticality and reduced certification costs.

#### 1.1.1. COST-EFFECTIVE DESIGN OF EMBEDDED **SYSTEMS**

Designing embedded systems often requires hardware-software co-design for a product that will sell only tens of thousands of units. This small volume makes design too expensive with today's tools. To overcome this, more powerful design tools are needed that can reduce the time to adapt or create new designs, particularly through integration and cross-unit optimization.

The integration of multiple functions on generic hardware (often commodity multi-core platforms) is a compelling avenue for reducing design costs. However, this approach requires that the safety requirements of the individual functions can still be guaranteed in the presence of other active functions on the same hardware. There is a need for defining standard methodologies for the design of such mixed criticality systems and support for reducing their cost of certification.

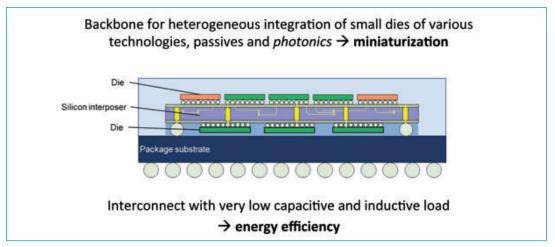

Designing application-specific hardware and selecting key parts to integrate (e.g., processors, memory, analog, wireless, sensors, MEMS) can enable more optimized devices. However, as the development cost and mask cost for producing silicon chips is prohibitive for small product quantities, new techniques should be developed to enable developers differentiate hardware with a reduced development cost. Solutions such as integration of heterogeneous dies on a silicon interposer might allow differentiation while using the existing technological capabilities of the European semiconductor industry.

#### 1.1.2. COST-EFFECTIVE CERTIFICATION

In sectors that deal with safety critical processes, embedded systems need to be certified before they can be deployed. The certification process is slow and costly. To increase the functionality and integration of embedded systems in safety critical applications we need to find ways to reduce the burden of certification. We should strive for a path to reduce certification, maintenance, and running costs.

For long-lived critical systems, such as airplane or train controllers, the cost of certification is so high that manufacturers are forced to stockpile replacement parts for the life of the product to avoid having to re-certify on new hardware. This requirement is extremely expensive, but could be avoided by enabling certification on virtual platforms. Such a certification would

allow manufacturers to substitute one certified virtual platform for another while maintaining certification. This would avoid the need to stockpile replacement parts and enable manufacturers to upgrade platforms to newer devices, which could reduce weight and energy requirements without requiring recertification.

Similarly, the development of new computing paradigms and development methodologies that are driven by the constraints of safety-critical systems (e.g. taking into account time requirements, latency) can reduce the qualification and verification cost by ensuring correct-by-construction designs. This approach differs significantly from the majority of mainstream computing approaches, which strive for best-effort average case performance, and ignore many safety-critical functional requirements such as timing.

#### 1.1.3. SECURE EMBEDDED SYSTEMS

The world of embedded systems has not been exposed to massive malware attacks in the past due to the general lack of external connectivity for embedded machines. However, today's systems are almost universally connected, and many high-profile hacking incidents have demonstrated that security needs to be improved in industrial and commercial embedded systems. Addressing this by hardware or software solutions will require a new focus on providing default security and updates for embedded systems ranging from industrial controllers to cars, pacemakers, televisions, refrigerators, smart meters, and even traffic lights.

#### 1.2. STRATEGIC AREA 2: **DATA CENTER COMPUTING**

Applications are moving towards global-scale services, accessible across the world and on all devices. Low power processors, systems, and communications are key to computing at this scale. Europe's strengths in low-power embedded computing forms a strong foundation for becoming the leader in energy efficient data center computing infrastructure. This leadership will allow us to bring more European technologies and innovations into the global market for data center compute storage and cloud systems.

#### 1.2.1. LOW-POWER MICRO SERVERS AND **MODULES**

Europe is currently the world leader for low power processors for mobile devices and is increasing its market share in microcontrollers for embedded systems and the Internet of Things. Moving beyond the embedded market, ARM has recently introduced its first 64-bit architecture to enable energy efficient server-class processors.

From a software point of view, efficient approaches for porting and optimizing existing data center software (typically written for x86 processors) to new energy efficient computing platforms will be required. Techniques for this transition include compiler optimization of binaries and libraries, dynamic recompilation, and even high-speed emulation or virtualization.

The goal of data center computing is to handle vast quantities of data efficiently and cheaply, storing and accessing data while minimizing cost and energy. This kind of workload is radically different from desktop, mobile, and HPC workloads. The hardware has to be adapted to the new workloads, and at the same time, the software has to be adapted to make optimal use of the resources offered by low-power server modules.

One opportunity to improve the hardware is the integration of efficient sever-class processors with innovative technologies such as 3D integration (e.g. stacking memory chips directly on top of processors) or 2.5D integration (processors and memory integrated on a fast silicon interposer, potentially including optical interconnect). This presents an opportunity for Europe to produce very efficient computing "bricks". Such "bricks" can form the basis for highly efficient cloud servers and low-power microservers. The micro-server form factor can provide extremely dense, small form-factor data center computing that can be installed anywhere without special infrastructure for cooling or power. These systems are of great interest for both large-scale data centers wishing to increase density and energy efficiency, and for small-scale operations, which may wish to keep their data physically on-site. However, the very high integration of these devices may require the development of new technologies for cooling (e.g., fluidic chip/wafer-level cooling), packaging, and interconnect.

#### 1.2.2. NETWORK AND STORAGE I/O

Network communication and storage are at the heart of modern data centers and play a critical role in both scaling and efficiency. Achieving the required I/O rates to keep processors busy in large servers is essential for handling big data workloads. Achieving the required storage I/O performance, density, energy efficiency, and overall reliability, will require the use of new storage technologies, including non-volatile memories (NVM) and new approaches to scaling the I/O subsystem. Software and hardware techniques for coping with I/O latencies will also need to be improved. New technologies are needed for improving the performance and energy efficiency of high-speed networking, including host protocols, optical interconnects, network interfaces, links, switches, and topologies. In addition we must address the overhead of I/O virtualization in servers with increasing core counts.

#### 1.3. STRATEGIC AREA 3: MOBILE SYSTEMS

The evolution of mobile devices will only accelerate as they become more powerful. New features will increasingly assist us with our daily tasks, anticipate our needs from our environment, and provide new capabilities, such as mobile payments and health and environmental monitoring. The value of these systems will come from their ability to integrate data from embedded sensors around the user and the world, process it in data centers, and deliver it directly to us in an intuitive and timely manner.

## 1.3.1. SUPPORTING IMMERSIVE/NATURAL INTERFACES

The key to the success of today's mobile devices has been in their smooth integration of remote data with their users' mobility. Natural interfaces, using human senses and interactions are important. Applications are beginning to use gesture, voice and image recognition and analysis as major sources of input to integrate more seamlessly with their user and environment. These more "natural" modalities augment information from traditional sensors such as Global Positioning Systems (GPS), compasses, gyroscopes, and accelerometers. On the output side, the graphics capabilities of mobile devices are making virtual or augmented reality practical. The end result of this progression will be devices that "disappear" into their environment by seamlessly adapting and providing the right data in the right context.

For the users, the mobile devices must support a smooth integration with data center processing and services to retrieve and process relevant information. However, much of the visualization and sensor pre-processing will happen on the mobile devices to reduce communication bandwidth. These functions, which deal with image processing, recognition and synthesis, will drive future hardware performance requirements, and delivering the seamless integration of embedded, mobile, and data center will demand significant advances in global-scale software development techniques.

## 1.3.2. ENSURING SECURITY AND PRIVACY FOR PERSONAL DEVICES

Ensuring the security and protection of personal data on mobile devices is a significant challenge. Separation of security domains between applications and between user contexts (e.g., professional and personal), private data, security against data theft, and secure payments are elements that should be developed. The solutions to these problems require cross-domain integration between the hardware, mobile device software, and data center applications. This will require the development of standards to enforce security and segregation of data, and provide for interoperability and validation.

#### 1.4. CROSS-CUTTING CHALLENGE 1: **ENERGY EFFICIENCY**

All computing systems are power-constrained today: either by battery capacity, energy cost, or cooling. Addressing energy efficiency in embedded, mobile, and data center computing is essential for providing increases in performance.

| Data center          | Mobile computing   | Embedded             |

|----------------------|--------------------|----------------------|

| computing            |                    | computing            |

| Data centers/        | Reduced energy     | Energy usage         |

| supercomputers       | consumption is     | determines the       |

| are extremely        | needed to increase | lifetime of battery- |

| power hungry.        | battery life for   | powered sensors      |

| More power-          | mobile devices     | and the extent of    |

| efficient solutions  |                    | their computa-       |

| (e.g. micro-servers) |                    | tional capabilities  |

| will reduce energy   |                    |                      |

| and cooling costs    |                    |                      |

| Power determines     | Passive cooling    | Many sensors have    |

| the maximum          | limits the         | limited ability to   |

| computing density    | maximum power      | dissipate power      |

| in a data center     | dissipation of a   | (e.g., industrial or |

| and the cost of      | mobile device      | sealed sensors)      |

| cooling              |                    |                      |

| infrastructure       |                    |                      |

The power per transistor has ceased to decrease as we scale transistors to smaller and smaller sizes. This presents us with the difficult problem that modern chips can consume more power than we can either provide or afford to cool. To continue to take advantage of larger numbers of smaller transistors, we need to figure out how to build hardware and write software to make optimal use of these transistors.

#### 1.4.1. OPTIMIZING DATA MOVEMENT AND **COMMUNICATIONS**

Today data movement uses more power than computation. We are now living in a world where communicating and storing data is more expensive (in both power and performance) than computing on it. To adapt to this change, we need to develop techniques for exposing data movement in applications and optimizing them at runtime and compile time and to investigate communication-optimized algorithms. Data movement needs to be viewed across the whole stack, not just within the processor. There is also a need to re-evaluate architecture decisions on memory and compute in light of new technology constraints and applications, for example, in light of 3D stacking, silicon photonics and new non-volatile memories.

#### 1.4.2. PROGRAMMING HETEROGENEOUS PARALLEL PROCESSORS

The straightforward way to increase performance for a given power budget is to use special-purpose accelerators. Accelerators are processors optimized for particular tasks, which allows them to achieve significantly better energy efficiency at the cost of flexibility. However, a heterogeneous mix of different processors imposes a dramatic burden of complexity on the software, which now has to be optimized for different processors and has to intelligently decide where and how to execute. On top of this complexity, the variety and rapid rate of change of hardware make it very expensive to constantly adapt to new hardware generations. The current state of the art for heterogeneous development is not yet cost-effective.

To overcome the complexity and cost of heterogeneous system development, we need tools and techniques that provide power and performance portability, analyze software to provide actionable, high-level feedback to developers and runtime systems, and enable porting of legacy applications to modern hardware. The programmer should only express the concurrency of the application, and leave to the tools the mapping of the concurrency of the application into the parallelism of the hardware. Promising approaches include domain specific languages (DSLs), meta-languages, high-level intermediate representations with runtime optimization (JITs), combinations of runtime and static program analysis, and the pervasive use of metadata to provide context and hints to automatic optimization and mapping tools. Empirical program and architecture optimization combined with run-time adaptation and machine learning has demonstrated a high potential to improve performance, power consumption and other important metrics. However, these techniques are still far from widespread due to unbearably long exploration and training times, ever changing tools and interfaces, lack of a common methodology, and lack of unified mechanisms for knowledge building and exchange.

#### 1.4.3. DEVELOPING NEW COMPUTING **MODALITIES**

Techniques such as biologically inspired approaches, approximate algorithms, stochastic and probabilistic computing, and inmemory computation have the potential to produce more energy efficient systems by relaxing accuracy requirements. Some of these technologies may also be particularly relevant for addressing silicon reliability issues in future process generations.

At the most basic level, many alternatives exist to current CMOS devices, but no clear winners have emerged as of yet [Berstein]. These alternative devices have the potential to reach switching energies three orders of magnitude lower than standard CMOS [Cavin]. Among these approaches, some may require a complete

rethinking of the whole design space. For example, field-coupled nano-computing [Imreo6] offers ultra-low power computation and non-volatile behavior, but it uses the so-called "processing-in-wire" design paradigm, which is completely different from standard CMOS practices. The opportunity to rethink the whole system design in light of new technologies may lead to novel solutions for today's problems.

## 1.5. CROSS-CUTTING CHALLENGE 2: SYSTEM COMPLEXITY

Future applications will require integration across large distributed systems, comprising thousands of embedded, mobile, and data center devices. Enabling future software and hardware developers and system designers to work quickly and effectively at this scale will require developing tools and techniques to efficiently optimize across system boundaries for performance and energy, ensure correctness and dependability, and enforce security and privacy requirements.

| Data center computing                                                                                                                                                                  | Mobile computing                                                                                                     | Embedded computing                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Scale-out to<br>support global-<br>scale applications<br>and very large user<br>bases                                                                                                  | Optimize communications and computation for power consumption and user experience, particularly on wireless networks | For power efficiency<br>massive parallelism<br>is required (e.g.,<br>GPU, manycore)                                                           |

| Scale-out work-<br>loads and scale-out<br>programming<br>models. At-scale<br>debugging and<br>development,<br>where developers<br>support deployment<br>across thousands<br>of servers | Improved user experience through environmental awareness from sensor fusion and intelligent visualization            | Reduced resource utilization but improved reliability and increased network integration. Certified programming languages and design paradigms |

| Intelligent processing, data mining, and complex analysis and computation                                                                                                              | Media processing.<br>Recognition,<br>analysis and<br>synthesis.                                                      | Feature extraction,<br>hardware support<br>for reducing power<br>and real-time<br>requirements                                                |

| Large storage<br>arrays containing<br>unstructured data                                                                                                                                | Big media<br>processing (mostly<br>video)                                                                            | Data capture and reduction                                                                                                                    |

Programming the individual compute elements (data center, mobile, and embedded) in global-scale systems of thousands of nodes is simply not practical. We must develop methodologies and tools to allow the specification of the systems at a higher level, and relieve the developers of the need to manage the distribution of computation, communications, and storage. To enable cost-effective global-scale applications we need tools for simultaneous development and deployment "at scale", that is, across thousands of machines at once. Developers need to be able to work "at scale": debugging, testing, and profiling require languages, tools, and runtimes that support global-scale development and deployment. Tools for analyzing interdependencies and tracking performance through large multilayered systems are mandatory. To be effective, these tools need to tie customer-focused performance metrics to software design (e.g., not just bits and bytes but interactions and product outcomes).

To accomplish this "at-scale", we need to develop automatic or semi-automatic techniques to generate system-level architectures. These tools will use the application's requirements (throughput, latency, processing, storage, etc.) and the technology constraints (data center capacity, compute and communications efficiency, energy costs, etc.) to select resources and connectivity that optimize for performance, complexity, and power, and map the applications to the required resources. At the system-level, this includes data center compute, storage, and communications capacity, partitioning applications across data center, mobile, and embedded compute elements, and optimizing tradeoffs in battery life, communications, and performance. Such design space exploration tools can reduce the time and cost of globalscale system development by allowing the developers to concentrate on functionality instead of the architecture required to achieve it.

New methodologies need to be developed to reduce the time it takes to efficiently implement applications and algorithms. Promising approaches include domain specific languages (DSLs), meta-languages, high-level intermediate representations with runtime optimization (JITs), combinations of runtime and static program analysis, and the pervasive use of metadata to provide context and hints to automatic optimization and mapping tools.

#### 1.6. CROSS-CUTTING CHALLENGE 3: **DEPENDABILITY**

Global-scale systems are not only difficult to design and implement, but also difficult to prove safe and secure as are their components. However, given our increasing dependence on global-scale computing systems, we need to place more attention on the dependability of systems at all levels. A small mistake in a global system may easily lead to an incident with a worldwide impact.

| Data center computing                                                                                                  | Mobile computing                                           | Embedded computing                                                                                                |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Data security,<br>privacy                                                                                              | Trustworthiness,<br>security, anti-<br>tampering           | Physical security<br>and safety,<br>certification                                                                 |

| Redundancy,<br>statistical failure<br>prediction, high<br>availability                                                 | Replace on failure,<br>ensure privacy of<br>remaining data | Fault tolerance,<br>error resilience                                                                              |

| Mixture of batch<br>and real-time (e.g.,<br>power grids,<br>financial), latency<br>sensitive for user<br>interactivity | Low average<br>latency for user<br>interactivity           | Closed loop<br>sensors used in a<br>real-time setting.<br>Sensors in mobile<br>devices often are<br>not real-time |

Dependability will play an increasingly important role in the next generation computing systems as they become more complex and interconnected, and deal with increasingly sensitive and critical information (e.g., health records, financial information, power regulation, transportation, etc.). In addition to the increase in dependability issues from a functional point of view, the electronic-level reliability of processors, memories, and communications channels is decreasing due to continued transistor scaling.

Privacy and security have become central issues as increasingly large amounts of data are stored in global data centers. Technologies and protocols must be developed at the hardware and software level to enable private data (e.g., medical, financial, industrial information) to be safely stored and processed in public and semi-public data centers. This should cover encryption and security for virtual machines at the hardware and software level, hardware and operating system support for data retention and deletion laws, and cryptographic support for law-enforcement and national security. Technologies should be designed with attention to legal compliance requirements.

For embedded systems, security has become as important as safety. Cars, planes and trains are being designed according to stringent safety requirements, yet insecure access to these

systems puts them at risk to hacking. High-profile international hacking of industrial controllers and demonstrations of remote hacks into cars, pacemakers, and hotel door locks have brought the issue of embedded system security to the forefront.

As the embedded systems interact with the physical world, they have to deal with non-functional requirements such as response time and reliability coming from various sources that have various level of trustworthiness. Methods to correctly fuse unreliable data from different sources in order to obtain a higher correctness at system level are important. These issues have rising priorities as we start to put significant degrees of high performance computing in real-time control loops (such as for smart grids) and their dependability needs to be ensured. Oualifying and ensuring correctness of a complex system composed of independently designed, distributed elements is a major challenge and new methodologies for proof, validation, and test are required.

For mobile systems, security is becoming more critical as people store more of their private lives and personal information on mobile devices. This leads to serious privacy and security problems when the mobile systems are hacked, stolen, lost, or broken. In all of these cases the data must remain secure to protect the individual. The amount of malware for mobile phones is currently growing exponentially as their popularity increases. Companies are having a hard time preventing employees from brining their own mobile devices to work (BYOD, Bring Your Own Device), and the security implications of such untrusted devices on corporate networks is significant.

A global perspective on how to tackle dependability across all system layers and in all its facets is required. The implementation of dependability requirements should be done by automated tools based on the developer's specifications. Manual implementation of safety, security, and reliability features is error-prone and makes certification difficult. Retraining all software developers as security experts is simply not feasible and even more difficult than to retrain them as parallel programmers.

## 1.7. POLICY RECOMMENDATION: SUPPORTING INSTRUMENTS

HiPEAC's industrial partners have identified several ways in which publicly funded research partnerships are particularly relevant for companies:

- They enable investments in new or high-risk areas where the business case is not yet clear (this is particularly valuable for SMEs, which have limited financial resources to back exploratory product development and research).

- They provide resources to develop an ecosystem around existing technology, even if such an ecosystem will benefit competitors as well.

However, core technologies will continue to be developed internally due to intellectual property rights concerns.

The supporting instruments in Horizon 2020 should assist in areas where the markets will not, and should encourage academic-industrial partnerships, transfer of research results into pilot lines or to European companies ready to productize them, and cooperation across borders.

#### 1.7.1. SUPPORTING VIRTUAL VERTICALIZATION

Supporting instruments should strive to bring together actors along the whole value chain to enable them to optimize across boundaries through close cooperation. Projects should explicitly seek players through most of the value chain from development to production and to the consumer in order to develop an ecosystem that can strengthen all companies together by delivering a compelling experience to the end user.

## 1.7.2. CONTINGENT FUNDING FOR COMMERCIAL DEVELOPMENT

The instruments should provide extended funding options contingent on a promising business case. This would allow projects to develop the project technologies and then re-evaluate whether they are commercializable. For example, by promoting the construction of demonstrators for field tests, or by a funding strategy with an option of 1-year commercialization extension for a subset of the partners.

## 1.7.3. CONTINUED FUNDING FOR ACADEMIC RESEARCH

The 3-year project is often too short for academic research. Providing a longer-term research instrument would allow academics to look into more risky projects. Currently the only option is

the European Research Council (ERC), which supports projects with a single principal investigator. The computing systems community in Europe is lacking the highly visible research labs that can attract international talent, serve as research hubs for industry, and provide incubators for new companies. There are a number of successful national initiatives like the excellence clusters funded by the German government. We believe that it makes sense to try to create and support a small number focused, physical 'eurolabs' with substantial funding for longer-term research.

#### 1.7.4. INTERNATIONAL COLLABORATION

International collaboration outside of Europe is necessary when key competencies are not present in Europe. Such collaboration should be carefully chosen in order to maintain industrial competitiveness of Europe, while promoting access to external competencies and facilities.

## 1.7.5. DEVELOPING PILOT-LINE FABRICATION CAPABILITIES

Niche market (10k-100k devices) startups and SMEs have an extremely difficult time producing hardware or Application Specific Integrated Circuit (ASIC) to demonstrate their product. In addition to the cost of the Computer Aided Design (CAD) tools needed to design the chips, the low volumes make them unattractive customers for existing foundries. This effect stifles development of new hardware ideas. Creating a European "hardware competence center" that offers affordable access to design tools and silicon runs, could help the emergence of creativity and new markets for European companies. Such silicon runs could be done either as "test lots" to validate the design or on pilot lines specialized for small quantities (e.g. using direct etching techniques instead of masks, to reduce the major source of cost in advanced technologies).

## 1.7.6. SPECIAL LICENSES (NON-GPL) FOR COLLABORATIVE PROJECTS

Not all Open Source and Free Software licenses are compatible with all business models. In particular the GNU General Public License (by design) can make it hard for proprietary software vendors to leverage code. Releasing the results from publicly funded projects at least under an additional license that makes such integration easier, such as the Modified BSD or MIT license, can help alleviate these problems. Publically funded projects should also strive to maintain clear licensing and copyright guidelines and contact information for commercial use of their products.

# THE HIPEAC VISION FOR ADVANCED COMPUTING IN HORIZON 2020: RATIONALE

Computing systems have become integrated global-scale systems with a tremendous economic impact. Today's driving applications require extensive integration of multiple systems and computing elements, with different levels of processing power, storage, and communication to provide rapid access to data and intelligent analysis. This section explores the market trends driving this development and their implications for computing systems in Europe.

The combination of massive amounts of unstructured data generated by numerous devices, a demand for intelligent processing and ubiquitous interconnection, strong guarantees of security, privacy, and trustworthiness, and an increasingly limited energy budget lead us to summarize the current trends in computing system applications as:

"An environment of efficient, intelligent, trustworthy, interconnected devices at your service".

To meet the challenges posed by these trends we need to enable global optimization of storage, communications, and processing with orders of magnitude less energy than today.

#### 2.1. APPLICATION PULL: "THE INDUSTRIAL INTERNET"

In the past three years we have witnessed a dramatic shift from "computers" to "mobile devices". Smart phones and tablets now dominate the consumer market, while desktop computer sales are decreasing, leading to a "Post-PC world" with the key characteristic of pervasive connectivity.

The key categories of computing devices in this new world of pervasive connectivity are:

- Data center computing: clouds, servers, HPC systems, and largescale storage systems, which are located in large-scale data centers and accessed remotely by users. The trend is towards providing computation as a utility that can be purchased from multiple vendors to fit the needs of the user.

- Mobile computing: PCs, tablets, mobile devices, and smart phones form the primary means of human-computer interaction. The trend is towards increasingly "humanized" interfaces, such as the use of natural language communication, vision, and gesture recognition.

- Embedded computing: "invisible" (for users) computing elements and (deeply-) embedded systems, including lowpower, often single-purpose, computing systems that are typically tightly coupled to sensors and actuators. The trend is towards higher levels of functional integration while maintaining critical performance.

These three types of computing devices combine to form the Industrial Internet: "a network that binds together intelligent machines, software analytics and people... [to improve] productivity and growth." [Annun12] The integration of these devices requires pervasive connectivity for nearly all tasks. For example, a mobile phone may read a Radio-Frequency Identification (RFID) tag, look up the product information from a server, and use that information to search for product reviews for the user. Without all three types of computing and ubiquitous connectivity, these services cannot function.

#### THE "INDUSTRIAL INTERNET" REVOLUTION

According to the CEO of General Electric, "The real opportunity for change is still ahead of us, surpassing the magnitude of the development and adoption of the consumer Internet. It is what we call the "Industrial Internet," an open, global network that connects people, data and machines. The Industrial Internet is aimed at advancing the critical industries that power, move and treat the world."

"The vast physical world of machines, facilities, fleets and networks can more deeply merge with the connectivity, big data and analytics of the digital world. This is what the Industrial Internet Revolution is all about."

"The Industrial Internet leverages the power of the cloud to connect machines embedded with sensors and sophisticated software to other machines (and to us) so we can extract data, make sense of it and find meaning where it did not exist before. Machines—from jet engines to gas turbines to CT scanners—will have the analytical intelligence to self-diagnose and self-correct. They will be able to deliver the right information to the right people, all in real time. When machines can sense conditions and communicate, they become instruments of understanding. They create knowledge from which we can act quickly, saving money and producing better outcomes."

From http://gigaom.com/2012/11/28/the-future-of-the-internet-is-intelligent-machines/

## 2.1.1. "POST-PC" DEVICES: THE LINK BETWEEN HUMANS AND CYBERSPACE

Tablets and mobile devices are gaining momentum and are quickly surpassing PCs as the primary form of consumer computing. The combination of their convenience, intuitive interface, and ability to access large amounts of online data has led to the Post-PC revolution. Consumers no longer perceive their smart phones or tablets as "computers", but rather as information and entertainment devices.

"Look at PCs...we sold more iPads last year than market leader HP sold of their entire PC lineup. There were about 120 million sold last year...projections suggest 375 million within four years. Will exceed PC sales."

Tim Cook, Apple CEO

Mobile devices are now the main interface between humans, the real physical world and the online "cyberspace". Pictures, movies, location data, etc., are created, manipulated and viewed through these devices, and count for a major part of the data exchanged on the internet. One important factor of their success is that they are "bigger on the inside than on the outside" thanks to their constant connectivity. This allows the user to have access to all the data on the internet, rather than being limited to the data stored locally. The success of mobile devices also resides in the fact that their interface is more natural for humans than a keyboard and mouse. Touch screens, gesture recognition (e.g. Microsoft's Kinect), voice control (e.g. by Apple's "Siri"), haptic feedback, and life-like imaging are providing natural interaction and are following the growing expectation that technology should be humanized and natural. We can expect that vision will be the next step in that direction, with devices "understanding" image content and their visual surroundings, and with new display technologies, glasses, and active-contacts leading to compelling reality augmentation.

Next generation devices will use more and more natural sensory interaction to improve their understanding of our intentions and requirements, delivering a personalized and unique interaction. These devices will be aware of their surroundings, which will enable them to empathize with and understand their user. This awareness will require merging and understanding data from an increasing number of other devices and sensors, including the user's personal data, to provide the most compelling user experience. Such trends will drive advances in processing power and data security and privacy.

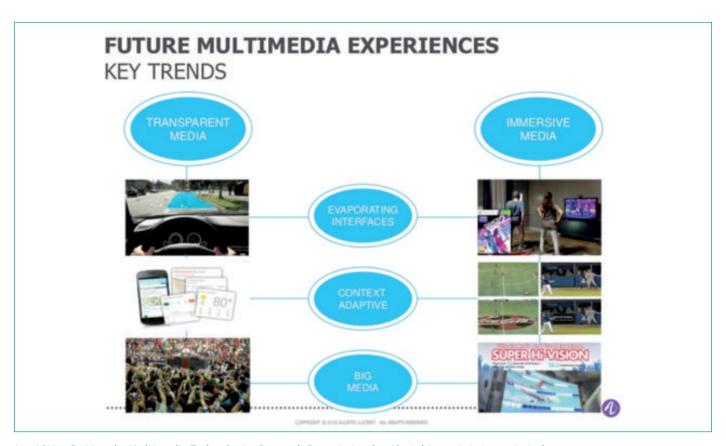

#### 2.1.2. NATURAL INTERFACES

Computing interfaces are becoming more natural. Users increasingly expect to use voice and touch-based controls with mobile phones and tablets. Text-to-speech and voice recognition services are improving rapidly and are being applied everywhere, from the automotive industry to public transportation, and as automated real-time translation services.

In the future, user interfaces will blend into the environment to form so-called "evaporating interfaces". Touch screens will have haptic feedback to simulate textures. Devices will be able to analyze and understand their auditory and visual environment, and sample the air to detect pollen and pollutants. Transparent heads-up displays are already used to overlay augmented reality in planes and high-end cars. Realistic avatars with advanced artificial intelligence will better understand the user and assist more efficiently — making manuals superfluous and manmachine interfaces more natural. Vision and image understanding will undoubtedly be the next major direction for device humanization and the entertainment industry will probably lead this evolution.

Ingrid Van De Voorde, Multimedia Technologies Research Domain Leader, Alcatel-Lucent, Antwerp iminds 2012

Cyber Systems (cloud, HPC, data servers), mobile and Cyber-physical Systems are all interconnected Courtesy Jan M. Rabaey. UC Berkeley, updated for this HiPEAC vision

#### 2.1.3. INTERACTION WITH THE PHYSICAL WORLD

Less apparent to the public is the explosion of embedded systems. These "small" systems are everywhere to gather information from the physical world, and yet they are nearly invisible. From the temperature sensor connected to a home thermostat to the dozens of embedded processors in cars, embedded data processing systems are invading our life by the billions. Their processing and communication capabilities are increasing by linking them to each other and to the Internet. This evolution enables increased functionality, such as internet-connected home thermostats that automatically learn your temperature preferences and allow remote operation. Indeed, it is becoming increasingly difficult to identify a single device where a complete application is running. Processing is now generally distributed between local pre-processing, processing for a user interface on a mobile device, and a live connection with the Internet for further processing or data collection from distant servers.

Embedded devices are increasingly interconnected, and communicate without human intervention. Kevin Ashton expressed this trend as follows: "If we had computers that knew everything there was to know about things – using data they gathered without any help from us – we would be able to track and count everything, and greatly reduce waste, loss and cost. We would know when things needed replacing, repairing or recalling, and whether they were fresh or past their best. The Internet of Things has the potential to change the world, just as the Internet did. Maybe even more so."

This global integration offers services and capabilities that were not possible before. For example, it can be used to save energy and resources ("smart grids") at a global or local level. In the case of electric cars, energy efficiency can be realized by creating an ecosystem where the car can be either recharged from a household power supply or provide energy to the local grid, depending on the current energy price. To optimize efficiency, the car uses information on traffic conditions and weather collected by embedded sensors to plan its route.

Computing systems will play a major role in healthcare, by monitoring wellness, identifying hazardous situations, and calling for help in emergencies.

More human-centric embedded systems will continue to evolve as well. In the near future it will be possible to check vital health parameters in real time, monitor activities and administer drugs in an adaptive manner. The performance of the human body may even be improved by enhancing certain functions such as hearing, vision and even smell (e.g. by warning a person to the presence of toxic particles). The augmentation of the human body through intelligent technology is colloquially referred to as "human++".

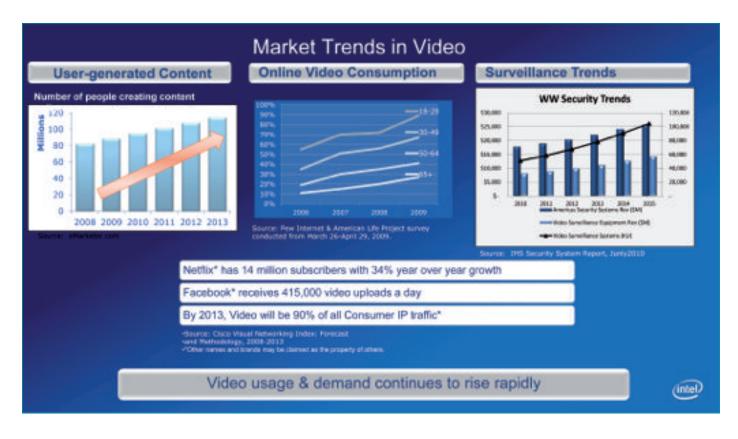

#### 2.1.4. DATA DELUGE

For the past decade, society has been generating exponentially increasing amounts of data. Commercial data sources include financial transactions, search histories, and product information. Public agencies contribute medical records, population databases, and legal and legislative data. Science and engineering routinely undertake large-scale simulations for weather prediction, drug discovery, product development, and record raw data from advanced sensors and experiments. There is also an exponential growth of data coming from data sensors (results of seismic data for oil exploration, genomic data in biology, etc.). Individuals are publishing an unprecedented amount of personal data, greatly encouraged by the explosion of social networking. This massive growth of data is forcing us to reevaluate how we work with data in computer systems.

## THE DATA CREATION BY RADIO ASTRONOMICAL FACILITIES

The LOw Frequency ARray (LOFAR), located in the Netherlands (Astron facilities), is a phased array radio telescope, in which the signals from a large collection of low cost antennae are combined into images. LOFAR has ~45,000 antennae, and produces 200-300 TB of data during a 6 hour observation (Throughput of 78 Gbit/s). The Square Kilometer Array (SKA) telescope, to be built in South Africa and Australia, will add at least one order of magnitude to these numbers.

This scale of scientific data is causing significant challenges for the radio astronomy community:

- Shipping high volumes of data (petabytes/day): the raw observation data is pre-processed locally to reduce the volume, but needs to be shipped to different centers for further analysis.

- Locality of processing vs. distributed processing: how to determine criteria (cost, energy, bandwidth)

- Complexity of process management: many antennae have to be controlled. Many data streams have to be routed to the processing facilities. For example, during pre-processing, those streams have to be coordinated in real time (the networks have insufficient buffer capacity to absorb more than a few "minutes" worth of data.)

- Data processing: the amount of computation per output is very large. There is an intricate interplay between hardware architecture and algorithms to process the large amounts of data in a "reasonable" amount of time,

- Graceful degradation/robustness: how to deal with failing hardware?

This data is not only a byproduct of our digital society, but also a valuable resource. Buried within this data are key insights into human behavior, market trends, diseases, engineering safety, environmental change, and the basic workings of physics. Yet with such a massive deluge of data it is becoming increasingly difficult to get the most from it, and to do so in a timely manner.

"The new resources of humanity are the data."

To exploit this data we need to be able to analyze it and respond in real time. Rapid analysis is key not only for financial trading (where a microsecond advantage can make the difference between a profit and a loss) and safety systems (where unknown delays can cause disaster), but also for delivering compelling customer experiences (by identifying trends early) and for society as a whole (identifying pandemics and optimizing transportation). Other opportunities are also emerging: massively instrumenting the energy grid in order to detect problems early to avoid general disasters. Reliable response time concerns are growing in data centers and HPC to avoid cascading delays caused by unpredictable response times.

The challenge for the next decade will be in coping with this humongous increase in data and the simultaneous demand for processing it faster and in due time.

#### **DATA DELUGE: A FEW FIGURES**

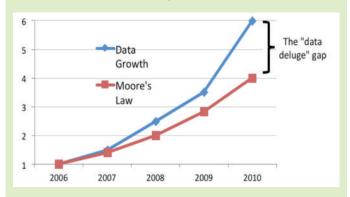

The term "Data Deluge" was coined in 2003 [Heyo3] in the context of scientific data management to describe the massive growth in the data volume generated in research (and by scientific instruments), which was rapidly dwarfing all the data previously collected in the history of research. Since then, the ability to generate vast quantities of data has outpaced the infrastructure and support tools. This is true for scientific data, digital media (audio and video), commercial transactions, social networks, legal and medical records, digital libraries, and so on. The need to analyze, organize, and sustain "big data" is one of the highest priorities in information technology across disciplines, organizations and geographies [E10].

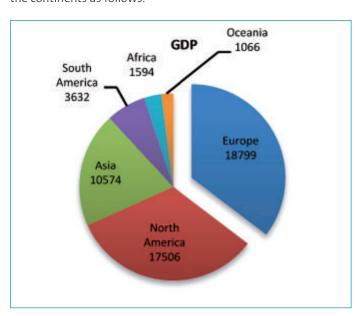

In 2010 the world generated over 1.2 Zettabytes (1021 bytes) of new data, 50% more than it had in all of human history before that. To put this in perspective, 120 Terabytes of new data was generated in the time it took to read the previous sentence. For example, Microsoft Update and Windows Update push out a Petabyte of updates monthly. Cisco predicts that by 2013 annual Internet traffic flowing will reach 667 Exabytes. A social network like Facebook produces 10TB/day of data, with Twitter is not far behind (7 TB/day); each of the 4.6B mobile phones